Os direitos autorais deste manual pertencem à Shenzhen Thinkcore Technology Co., Ltd. e todos os direitos são reservados. Quaisquer empresas ou indivíduos não estão autorizados a extrair parte ou todo este manual, e os infratores serão processados de acordo com a lei.

Os manuais da plataforma de desenvolvimento à venda serão atualizados de tempos em tempos, faça o download do manual mais recente no site www.think-core.com ou entre em contato com o representante de vendas da empresa, sem aviso prévio.

|

Versão |

Encontro |

Autor |

Descrição |

|

Rev.01 |

2022-08-04 |

|

Revisão |

TC-RK3568 Resumo da placa de desenvolvimento de furos de selo

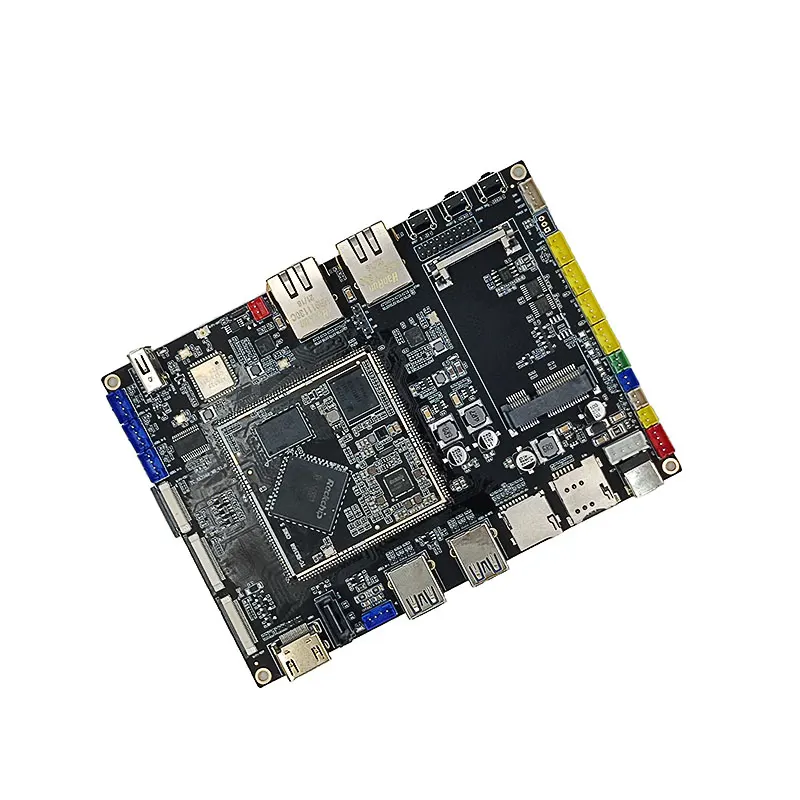

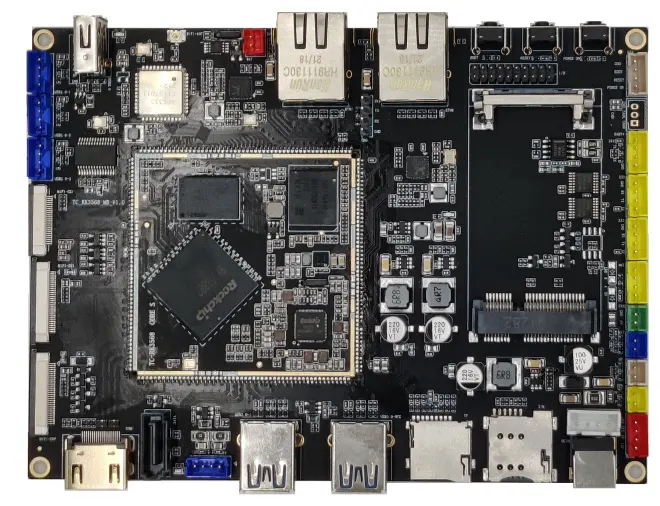

A placa de desenvolvimento de furo de carimbo TC-RK3568 inclui SOM de furo de carimbo TC-RK3568 e baord de suporte.

O sistema Stamp Hole TC-RK3568 no módulo está equipado com o processador Rockchip RK3568 de 64 bits, configurado com GPU dual-core e NPU de alto desempenho.

RK3568, o processador Cortex-A55 quad-core de 64 bits, com processo de litografia de 22 nm, possui frequência de até 2,0 GHz, oferecendo desempenho eficiente e estável para processamento de dados de equipamentos de back-end. Existem várias opções de armazenamento, permitindo que os clientes implementem rapidamente a pesquisa e a produção de produtos. Ele suporta até 8 GB de RAM, com largura de até 32 bits e frequência de até 1600 MHz. Ele suporta ECC de todos os links de dados, tornando os dados mais seguros e confiáveis e atendendo aos requisitos de execução de aplicativos de produtos de grande memória. Ele é integrado com GPU dual-core, VPU de alto desempenho e NPU de alta eficiência. A GPU suporta OpenGL ES3.2/2.0/1.1, Vulkan1.1. A VPU pode atingir decodificação de vídeo 4K 60fps H.265/H.264/VP9 e codificação de vídeo 1080P 100fps H.265/ H.264. O NPU oferece suporte à alternância com um clique de estruturas convencionais, como Caffe/TensorFlow.

Com MIPI-CSI x2, MIPI-DSI x2, HDMI2.0, interfaces de vídeo EDP, ele pode suportar até três saídas de tela com exibição diferente. O ISP 8M integrado suporta câmeras duplas e HDR. A interface de entrada de vídeo pode ser conectada a uma câmera externa ou a várias câmeras. É equipado com duas portas RJ45 Gigabit Ethernet adaptáveis, através das quais os dados da rede interna e externa podem ser acessados e transmitidos, melhorando a eficiência da transmissão da rede e atendendo às necessidades de produtos com várias portas de rede, como NVR e gateway industrial.

A placa transportadora inclui muitas interfaces, como porta 4G LTE, USB3.0, USB2.0, PCIE, Ethernet dupla, WIFI, Bluetooth, entrada e saída de áudio, saída HDMI, exibição MIPI DSI, exibição eDP, exibição LVDS, MIPI CSI câmera, slot para cartão TF, RS485, RS232, TTL, CAN, saída de energia, SATA, etc.

Android 11, Ubuntu 18.04 OS, Debian OS e Linux Buildroot são suportados. A operação estável e confiável fornece um ambiente de sistema seguro e estável para pesquisa e produção de produtos.

Um SDK completo, documentos de desenvolvimento, exemplos, documentos de tecnologia, tutoriais e outros recursos são fornecidos para os usuários fazerem uma personalização adicional.

Tamanho: 150mm x 110mm.

Interfaces ricas, podem ser usadas diretamente em vários produtos inteligentes para facilitar a conclusão dos produtos.

Android 11.0, Ubuntu 18.04 OS, Debian OS e Linux Buildroot são suportados.

Esta placa pode ser amplamente utilizada em NVRs inteligentes, terminais em nuvem, gateways IoT, controle industrial, computação de ponta, portões de reconhecimento facial, NASs, consoles centrais de veículos, etc.

|

Especificações |

|

|

CPU |

RockChip RK3568, Quad-core Cortex-A55 de 64 bits, processo de litografia de 22 nm, frequência de até 2,0 GHz |

|

GPU |

ARM G52 2EE Suporta OpenGL ES 1.1/2.0/3.2, OpenCL 2.0, Vulkan 1.1 Hardware de aceleração 2D de alto desempenho incorporado |

|

NPU |

0.8Tops@INT8, acelerador AI integrado de alto desempenho RKNN NPU Suporta comutação de um clique de Caffe/TensorFlow/TFLite/ONNX/PyTorch/Keras/Darknet |

|

VPU |

Suporta decodificação de vídeo 4K 60fps H.265/H.264/VP9 Suporta codificação de vídeo 1080P 100 fps H.265/H.264 Suporta 8M ISP, suporta HDR |

|

BATER |

2GB/4GB/8GB |

|

Armazenar |

8 GB/16 GB/32 GB/64 GB/128 GB eMMC Suporta SATA 3.0 x 1 (expandir com SSD/HDD de 2,5â) Suporta TF-Card Slot x1 (Expandir com cartão TF) |

|

sistema operacional |

Android11/Linux Buildroot/Ubuntu/Debian |

|

Recursos de hardware |

|

|

Tela |

1 * HDMI2.0, suporta saída 4K@60fps 1 * MIPI DSI, suporta saída 1920*1080@60fps 1 * LVDS, suporta saída 1920*1080@60fps 1 * eDP1.3, suporta saída de 2560x1600@60fps |

|

Ethernet |

Suporta duas portas Gigabit Ethernet (1000 Mbps) |

|

Wi-fi |

Mini PCIe para conectar 4G LTE Suporta Wi-Fi 6 (802.11 AX) Suporta BT5.0 |

|

PCIE3.0 |

Suporta interface PCE3.0 |

|

áudio |

1 * saída de áudio HDMI 1 * saída de alto-falante 1 * saída de fone de ouvido 1 * entrada de áudio a bordo do microfone |

|

Câmera |

Suporta interface de câmera MIPI-CSI de 1 canal Suporta HDR, a imagem permanece clara sob luz de fundo ou condições de luz forte

|

|

USB |

1 * host USB 3.0, 4 * host USB 2.0, 1 * USB 3.0 OTG |

|

SATA |

1 * SATA, 6,0 Gb/s |

|

Serial |

1 * TTL, 2 * RS232, 1 * RS485 |

|

POSSO |

Suporta CAN2.0B, Suporta 1Mbps, 8Mbps |

|

Cartão TF |

1 * Slot para cartão TF |

|

Outras |

GPIO e ADC |

|

Tamanho |

150mm * 110mm |

|

|

|

|

Tensão de entrada |

12V/3A |

|

Temperatura de armazenamento

|

-30~80Â |

|

Temperatura de operação |

-20~60Â |

|

Umidade de Armazenamento |

10%~80% |

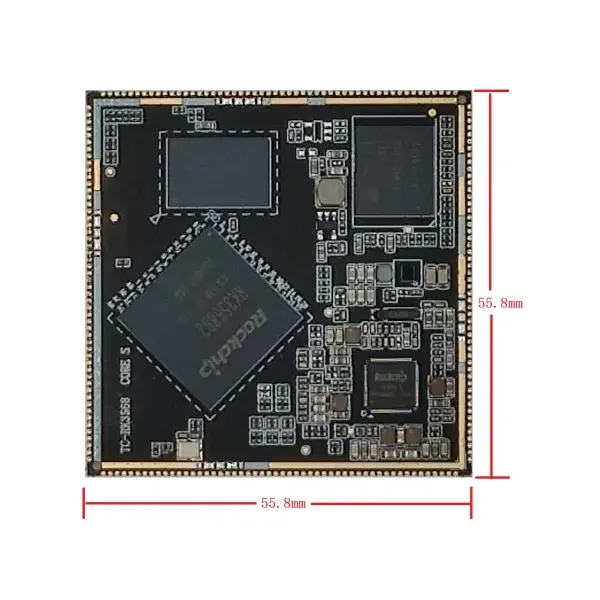

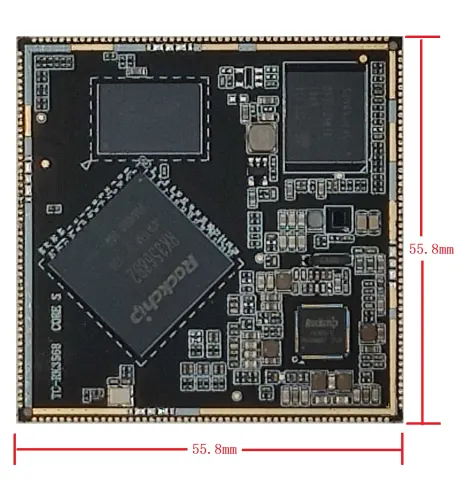

Frente SOM

|

PIN |

Definição de pinos da placa principal |

função padrão |

Descrição da função padrão |

Potência I/O |

Tipo de almofada IO pull |

|

1 |

VCC3V3_SYS |

Fonte de alimentação do sistema de 3,3 V |

Tensão de entrada 3,3V |

|

- |

|

2 |

VCC3V3_SYS |

Fonte de alimentação do sistema de 3,3 V |

Tensão de entrada 3,3V |

|

- |

|

3 |

GND |

GND |

GND |

|

- |

|

4 |

GND |

GND |

GND |

|

- |

|

5 |

SDMMC0_DET_L |

SDMMC0_DET/SATA_CP_DET/PCIE30X1_CLKREQn_M0/GPIO0_A4_u |

entrada de detecção SDMMC0 |

3,3V |

E/S PARA CIMA |

|

6 |

SDMMC0_D3 |

SDMMC0_D3/ARMJTAG_TMS/UART5_RTSn_M0/GPIO2_A0_u |

porta de dados SDMMC0 |

3,3V |

E/S PARA CIMA

|

|

7 |

SDMMC0_D2 |

SDMMC0_D2/ARMJTAG_TCK/UART5_CTSn_M0/GPIO1_D7_u |

porta de dados SDMMC0 |

3,3V |

E/S PARA CIMA

|

|

8 |

SDMMC0_D1 |

SDMMC0_D1/UART2_RX_M1/UART6_RX_M1/PWM9_M1/GPIO1_D6_u |

porta de dados SDMMC0 |

3,3V |

E/S PARA CIMA

|

|

9 |

SDMMC0_D0 |

SDMMC0_D0/UART2_TX_M1/UART6_TX_M1/PWM8_M1/GPIO1_D5_u |

porta de dados SDMMC0 |

3,3V |

E/S PARA CIMA

|

|

10 |

SDMMC0_CMD |

SDMMC0_CMD/PWM10_M1/UART5_RX_M0/CAN0_TX_M1/GPIO2_A1_u |

Saída do comando SDMMC0 |

3,3V |

E/S PARA CIMA

|

|

11 |

SDMMC0_CLK |

SDMMC0_CLK/TEST_CLKOUT/UART5_TX_M0/CAN0_RX_M1/GPIO2_A2_d |

Saída de relógio SDMMC0

|

3,3V |

E/S PARA BAIXO |

|

12 |

REINICIALIZAR |

NPOR_U |

Detecção de sinal de reinicialização |

3,3V |

- |

|

13 |

RK809_PWRON |

Ligar |

Entrada de sinal de alimentação, chave de alimentação de conexão externa, baixa ativa |

|

- |

|

14 |

RECUPERAÇÃO |

SARADC_VIN0 |

Entrada de teclado AD |

1,8V |

- |

|

15 |

EXT_EN |

EXT_EN |

Ativação de energia PMIC |

|

- |

|

16 |

HPR_OUT |

HPR_OUT |

Fone de ouvido direto |

3,3V |

- |

|

17 |

HPL_OUT |

HPL_OUT |

Fone de ouvido deixado de fora |

3,3V |

- |

|

18 |

SPKP_OUT |

SPKP_OUT |

Fala |

5V/0,6W |

- |

|

19 |

SPKN_OUT |

SPKN_OUT |

Fala- |

5V/0,6W |

- |

|

20 |

MIC1_INN |

MIC1_INN/MIC_R |

MIC1_INN |

3,3V |

- |

|

21 |

MIC1_INP |

MIC1_INP/MIC_L |

MIC1_INP |

3,3V |

- |

|

22 |

HP_DET_L_GPIO3_C2 |

LCDC_VSYNC/VOP_BT1120_D14/SPI1_MISO_M1/UART5_TX_M1/I2S1_SDO3_M2/GPIO3_C2_d |

detecção de fone de ouvido |

3,3V |

E/S PARA BAIXO |

|

23 |

SPK_CTL_H_GPIO3_C3 |

LCDC_DEN/VOP_BT1120_D15/SPI1_CLK_M1/UART5_RX_M1/I2S1_SCLK_RX_M2/GPIO3_C3_d |

|

3,3V |

E/S PARA BAIXO |

|

24 |

VCC3V3_SD |

Fonte de alimentação de 3,3 V |

Tensão de saída 3,3V para cartão SD, corrente de saída nominal 2A |

|

- |

|

25 |

VCC_3V3 |

Fonte de alimentação de 3,3 V |

Tensão de saída 3,3V, corrente de saída nominal 2A |

|

- |

|

26 |

VCC_1V8 |

Fonte de alimentação de 1,8 V |

Tensão de saída 1,8 V, corrente de saída nominal 2,5 A |

|

- |

|

27 |

PDM_SDI1_M0_ADC |

I2S1_SDO3_M0/I2S1_SDI1_M0/PDM_SDI1_M0/PCIE20_PERSTn_M2/GPIO1_B2_d |

PDM_SDI1_M0_ADC |

3,3V |

IO PARA BAIXO |

|

28 |

PDM_SDI2_M0_ADC |

I2S1_SDO2_M0/I2S1_SDI2_M0/PDM_SDI2_M0/PCIE20_WAKEn_M2/ACODEC_ADC_SYNC/GPIO1_B1_d |

PDM_SDI2_M0_ADC |

3,3V |

IO PARA BAIXO |

|

29 |

PDM_SDI3_M0_ADC |

I2S1_SDO1_M0/I2S1_SDI3_M0/PDM_SDI3_M0/PCIE20_CLKREQn_M2/ACODEC_DAC_DATAR/GPIO1_B0_d |

PDM_SDI3_M0_ADC |

3,3V |

IO PARA BAIXO |

|

30 |

PDM_CLK1_M0_ADC |

I2S1_SCLK_RX_M0/UART4_RX_M0/PDM_CLK1_M0/SPDIF_TX_M0/GPIO1_A4_d |

PDM_CLK1_M0_ADC |

3,3V |

IO PARA BAIXO |

|

31 |

GMAC0_TXD0 |

GMAC0_TXD0/UART1_RX_M0/GPIO2_B3_u |

dados de transmissão GMAC0 |

1,8V |

E/S PARA CIMA |

|

32 |

GMAC0_TXD1 |

GMAC0_TXD1/UART1_TX_M0/GPIO2_B4_u |

dados de transmissão GMAC0 |

1,8V |

E/S PARA CIMA |

|

33 |

GMAC0_TXD2 |

SDMMC1_D3/GMAC0_TXD2/UART7_TX_M0/GPIO2_A6_u |

dados de transmissão GMAC0 |

1,8V |

E/S PARA CIMA |

|

34 |

GMAC0_TXD3 |

SDMMC1_CMD/GMAC0_TXD3/UART9_RX_M0/GPIO2_A7_u |

dados de transmissão GMAC0 |

1,8V |

E/S PARA CIMA |

|

35 |

GMAC0_TXEN |

GMAC0_TXEN/UART1_RTSn_M0/SPI1_CLK_M0/GPIO2_B5_u |

GMAC0 habilitar transmissão |

1,8V |

E/S PARA CIMA |

|

36 |

GMAC0_TXCLK |

SDMMC1_CLK/GMAC0_TXCLK/UART9_TX_M0/GPIO2_B0_d |

relógio de transmissão GMAC0 |

1,8V |

E/S PARA BAIXO |

|

37 |

GMAC0_RXD0 |

GMAC0_RXD0/UART1_CTSn_M0/SPI1_MISO_M0/GPIO2_B6_u |

GMAC0 receber dados |

1,8v |

E/S PARA CIMA |

|

38 |

GMAC0_RXD1 |

I2S2_SCLK_RX_M0/GMAC0_RXD1/UART6_RTSn_M0/SPI1_MOSI_M0/GPIO2_B7_d |

GMAC0 receber dados |

1,8V |

E/S PARA BAIXO |

|

39 |

GMAC0_RXD2 |

SDMMC1_D0/GMAC0_RXD2/UART6_RX_M0/GPIO2_A3_u |

GMAC0 receber dados |

1,8v |

E/S PARA CIMA |

|

40 |

GMAC0_RXD3 |

SDMMC1_D1/GMAC0_RXD3/UART6_TX_M0/GPIO2_A4_u |

GMAC0 receber dados |

1,8V |

E/S PARA CIMA |

|

41 |

GMAC0_RXDV_CRS |

I2S2_LRCK_RX_M0/GMAC0_RXDV_CRS/UART6_CTSn_M0/SPI1_CS0_M0/GPIO2_C0_d |

Sinal válido de dados GMAC0 RX |

1,8V |

E/S PARA BAIXO |

|

42 |

GMAC0_RXCLK |

SDMMC1_D2/GMAC0_RXCLK/UART7_RX_M0/GPIO2_A5_u |

relógio de recepção GMAC0 |

1,8V |

E/S PARA CIMA |

|

43 |

ETH0_REFCLKO_25M |

I2S2_MCLK_M0/ETH0_REFCLKO_25M/UART7_RTSn_M0/SPI2_CLK_M0/GPIO2_C1_d |

ETH0_REF CLOCK OUTPUT_25MHz CPU para PHY, NC padrão |

1,8V |

E/S PARA BAIXO |

|

44 |

GMAC0_MCLKINOUT |

I2S2_SCLK_TX_M0/GMAC0_MCLKINOUT/UART7_CTSn_M0/SPI2_MISO_M0/GPIO2_C2_d |

relógio externo GMAC0 |

1,8V |

E/S PARA BAIXO |

|

45 |

GMAC0_MDC |

I2S2_LRCK_TX_M0/GMAC0_MDC/UART9_RTSn_M0/SPI2_MOSI_M0/GPIO2_C3_d |

relógio de gerenciamento MAC0 |

1,8V |

E/S PARA BAIXO |

|

46 |

GMAC0_MDIO |

I2S2_SDO_M0/GMAC0_MDIO/UART9_CTSn_M0/SPI2_CS0_M0/GPIO2_C4_d |

Comando e dados de gerenciamento MAC0 |

1,8V |

E/S PARA BAIXO |

|

47 |

GMAC0_RSTN_GPIO3_B7 |

LCDC_D21/VOP_BT1120_D12/GMAC1_TXD1_M0/I2C3_SDA_M1/PWM11_IR_M0/GPIO3_B6_d |

|

3,3V |

IO PARA BAIXO |

|

48 |

GMAC0_INT_PMEB_GPIO3_C0 |

LCDC_HSYNC/VOP_BT1120_D13/SPI1_MOSI_M1/PCIE20_PERSTn_M1/I2S1_SDO2_M2/GPIO3_C1_d |

|

3,3V |

E/S PARA BAIXO |

|

49 |

RTCTC_INT_L_GPIO0_D3 |

GPIO0_D3_d |

RTC_IC_INT, ativo baixo |

1,8V |

E/S PARA BAIXO |

|

50 |

I2C5_SDA_M0 |

LCDC_D19/VOP_BT1120_D10/GMAC1_RXER_M0/I2C5_SDA_M0/PDM_SDI1_M2/GPIO3_B4_d |

porta serial I2C 5 |

3,3V |

E/S PARA BAIXO |

|

51 |

I2C5_SCL_M0 |

LCDC_D18/VOP_BT1120_D9/GMAC1_RXDV_CRS_M0/I2C5_SCL_M0/PDM_SDI0_M2/GPIO3_B3_d |

porta serial I2C 5 |

3,3V |

E/S PARA BAIXO |

|

52 |

PWM3_IR |

PWM3_IR/EDP_HPDIN_M1/PCIE30X1_WAKEn_M0/MCU_JTAG_TMS/GPIO0_C2_d |

|

3,3V |

E/S PARA BAIXO |

|

53 |

CAN1_TX_M1 |

PWM15_IR_M1/SPI3_MOSI_M1/CAN1_TX_M1/PCIE30X2_WAKEn_M2/I2S3_SCLK_M1/GPIO4_C3_d |

transmissão de dados CAN |

3,3V |

E/S PARA BAIXO |

|

54 |

CAN1_RX_M1 |

PWM14_M1/SPI3_CLK_M1/CAN1_RX_M1/PCIE30X2_CLKREQn_M2/I2S3_MCLK_M1/GPIO4_C2_d |

dados CAN receber |

3,3V |

E/S PARA BAIXO |

|

55 |

UART2_RX_M0_DEBUG |

UART2_RX_M0/GPIO0_D0_u |

porta serial UART |

3,3V |

E/S PARA CIMA |

|

56 |

UART2_TX_M0_DEBUG |

UART2_TX_M0/GPIO0_D1_u |

Transmissão de dados da porta serial UART para depuração |

3,3V |

E/S PARA CIMA |

|

57 |

UART3_RX_M1 |

LCDC_D23/PWM13_M0/GMAC1_MCLKINOUT_M0/UART3_RX_M1/PDM_SDI3_M2/GPIO3_C0_d |

Recepção de dados da porta serial UART |

3,3V |

E/S PARA BAIXO |

|

58 |

UART3_TX_M1 |

LCDC_D22/PWM12_M0/GMAC1_TXEN_M0/UART3_TX_M1/PDM_SDI2_M2/GPIO3_B7_d |

Transmissão de dados da porta serial UART |

3,3V |

E/S PARA BAIXO |

|

59 |

UART4_TX_M1 |

LCDC_D17/VOP_BT1120_D8/GMAC1_RXD1_M0/UART4_TX_M1/PWM9_M0/GPIO3_B2_d |

Transmissão de dados da porta serial UART |

3,3V |

E/S PARA BAIXO |

|

60 |

UART4_RX_M1 |

LCDC_D16/VOP_BT1120_D7/GMAC1_RXD0_M0/UART4_RX_M1/PWM8_M0/GPIO3_B1_d |

Recepção de dados da porta serial UART |

3,3V |

E/S PARA BAIXO |

|

61 |

UART9_RX_M1 |

PWM13_M1/SPI3_CS0_M1/SATA0_ACT_LED/UART9_RX_M1/I2S3_SDI_M1/GPIO4_C6_d |

Recepção de dados da porta serial UART |

3,3V |

E/S PARA BAIXO |

|

62 |

UART9_TX_M1 |

PWM12_M1/SPI3_MISO_M1/SATA1_ACT_LED/UART9_TX_M1/I2S3_SDO_M1/GPIO4_C5_d |

Transmissão de dados da porta serial UART |

3,3V |

E/S PARA BAIXO |

|

63 |

UART7_RX_M1 |

PWM15_IR_M0/SPDIF_TX_M1/GMAC1_MDIO_M0/UART7_RX_M1/I2S1_LRCK_RX_M2/GPIO3_C5_d |

Recepção de dados da porta serial UART |

3,3V |

E/S PARA BAIXO |

|

64 |

UART7_TX_M1 |

PWM14_M0/VOP_PWM_M1/GMAC1_MDC_M0/UART7_TX_M1/PDM_CLK1_M2/GPIO3_C4_d |

Transmissão de dados da porta serial UART |

3,3V |

E/S PARA BAIXO |

|

65 |

RS485_DIR_GPIO3_B5 |

LCDC_D20/VOP_BT1120_D11/GMAC1_TXD0_M0/I2C3_SCL_M1/PWM10_M0/GPIO3_B5_d |

Direção de dados RS485 |

3,3V |

E/S PARA BAIXO |

|

66 |

DVP_PWREN0_H_GPIO0_B0 |

CLK32K_IN/CLK32K_OUT0/PCIE30X2_BUTTONRSTn/GPIO0_B0_u |

|

3,3V |

E/S PARA CIMA |

|

67 |

WIFI_PWREN_L_GPIO0_C1 |

PWM2_M0/NPUAVS/UART0_TX/MCU_JTAG_TDI/GPIO0_C1_d |

|

3,3V |

E/S PARA BAIXO |

|

68 |

I2S3_SDI_M0 |

LCDC_D13/VOP_BT1120_CLK/GMAC1_TXCLK_M0/I2S3_SDI_M0/SDMMC2_CLK_M1/GPIO3_A6_d |

I2S3_SDI |

3,3V |

E/S PARA BAIXO |

|

69 |

I2S3_SDO_M0 |

LCDC_D12/VOP_BT1120_D4/GMAC1_RXD3_M0/I2S3_SDO_M0/SDMMC2_CMD_M1/GPIO3_A5_d |

I2S3_SDO |

3,3V |

E/S PARA BAIXO |

|

70 |

I2S3_LRCK_M0 |

LCDC_D11/VOP_BT1120_D3/GMAC1_RXD2_M0/I2S3_LRCK_M0/SDMMC2_D3_M1/GPIO3_A4_d |

I2S3_LRCK |

3,3V |

E/S PARA BAIXO |

|

71 |

I2S3_SCLK_M0 |

LCDC_D10/VOP_BT1120_D2/GMAC1_TXD3_M0/I2S3_SCLK_M0/SDMMC2_D2_M1/GPIO3_A3_d |

I2S3_SCLK |

3,3V |

E/S PARA BAIXO |

|

72 |

HOST_WAKE_BT_H_GPIO3_A2 |

LCDC_D9/VOP_BT1120_D1/GMAC1_TXD2_M0/I2S3_MCLK_M0/SDMMC2_D1_M1/GPIO3_A2_d |

HOST_WAKE_BT |

3,3V |

E/S PARA BAIXO |

|

73 |

BT_WAKE_HOST_H_GPIO3_A1 |

LCDC_D8/VOP_BT1120_D0/SPI1_CS0_M1/PCIE30X1_PERSTn_M1/SDMMC2_D0_M1/GPIO3_A1_d |

BT_WAKE_HOST |

3,3V |

E/S PARA BAIXO |

|

74 |

BT_REG_ON_H_GPIO3_A0 |

LCDC_CLK/VOP_BT656_CLK_M0/SPI2_CLK_M1/UART8_RX_M1/I2S1_SDO1_M2/GPIO3_A0_d |

Ativação de energia do módulo Bluetooth |

3,3V |

E/S PARA BAIXO |

|

75 |

UART8_RX_M0 |

CLK32K_OUT1/UART8_RX_M0/SPI1_CS1_M0/GPIO2_C6_d |

Recepção de dados da porta serial UART |

1,8V |

E/S PARA BAIXO |

|

76 |

UART8_TX_M0 |

I2S2_SDI_M0/GMAC0_RXER/UART8_TX_M0/SPI2_CS1_M0/GPIO2_C5_d |

Transmissão de dados da porta serial UART |

1,8V |

E/S PARA BAIXO |

|

77 |

UART8_CTSN_M0 |

SDMMC1_DET/I2C4_SCL_M1/UART8_CTSn_M0/CAN2_TX_M1/GPIO2_B2_u |

UART8_CTSn_M0 |

1,8V |

E/S PARA BAIXO |

|

78 |

UART8_RTSN_M0 |

SDMMC1_PWREN/I2C4_SDA_M1/UART8_RTSn_M0/CAN2_RX_M1/GPIO2_B1_d |

UART8_RTSn_M0 |

1,8V |

E/S PARA BAIXO |

|

79 |

WIFI_REG_ON_H_GPIO3_D5 |

CIF_D7/EBC_SDDO7/SDMMC2_PWREN_M0/I2S1_SDI3_M1/VOP_BT656_D7_M1/GPIO3_D5_d |

WIFI_REG ativado |

1,8V |

E/S PARA BAIXO |

|

80 |

WIFI_WAKE_HOST_H_GPIO3_D4 |

CIF_D6/EBC_SDDO6/SDMMC2_DET_M0/I2S1_SDI2_M1/VOP_BT656_D6_M1/GPIO3_D4_d |

Host de despertar WIFI |

1,8V |

E/S PARA BAIXO |

|

81 |

SDMMC2_CLK_M0 |

CIF_D5/EBC_SDDO5/SDMMC2_CLK_M0/I2S1_SDI1_M1/VOP_BT656_D5_M1/GPIO3_D3_d |

relógio SDMMC2 |

1,8V |

E/S PARA BAIXO |

|

82 |

SDMMC2_CMD_M0 |

CIF_D4/EBC_SDDO4/SDMMC2_CMD_M0/I2S1_SDI0_M1/VOP_BT656_D4_M1/GPIO3_D2_d |

Comando SDMMC2 |

1,8V |

E/S PARA BAIXO |

|

83 |

SDMMC2_D3_M0 |

CIF_D3/EBC_SDDO3/SDMMC2_D3_M0/I2S1_SDO0_M1/VOP_BT656_D3_M1/GPIO3_D1_d |

dados SDMMC2 |

1,8V |

E/S PARA BAIXO |

|

84 |

SDMMC2_D2_M0 |

CIF_D2/EBC_SDDO2/SDMMC2_D2_M0/I2S1_LRCK_TX_M1/VOP_BT656_D2_M1/GPIO3_D0_d |

dados SDMMC2 |

1,8V |

E/S PARA BAIXO |

|

85 |

SDMMC2_D1_M0 |

CIF_D1/EBC_SDDO1/SDMMC2_D1_M0/I2S1_SCLK_TX_M1/VOP_BT656_D1_M1/GPIO3_C7_d |

dados SDMMC2 |

1,8V |

E/S PARA BAIXO |

|

86 |

SDMMC2_D0_M0 |

CIF_D0/EBC_SDDO0/SDMMC2_D0_M0/I2S1_MCLK_M1/VOP_BT656_D0_M1/GPIO3_C6_d |

dados SDMMC2 |

1,8V |

E/S PARA BAIXO |

|

87 |

GMAC1_INT/PMEB_GPIO3_A7 |

LCDC_D14/VOP_BT1120_D5/GMAC1_RXCLK_M0/SDMMC2_DET_M1/GPIO3_A7_d |

|

3,3V |

E/S PARA BAIXO |

|

88 |

GMAC1_RSTN_GPIO3_B0 |

LCDC_D15/VOP_BT1120_D6/ETH1_REFCLKO_25M_M0/SDMMC2_PWREN_M1/GPIO3_B0_d |

|

3,3V |

E/S PARA BAIXO |

|

89 |

GMAC1_MDIO_M1 |

IF_VSYNC/EBC_SDOE/GMAC1_MDIO_M1/I2S2_SCLK_TX_M1/GPIO4_B7_d |

comando e dados de gerenciamento GMAC1 |

1,8V |

E/S PARA BAIXO |

|

90 |

GMAC1_MDC_M1 |

CIF_HREF/EBC_SDLE/GMAC1_MDC_M1/UART1_RTSn_M1/I2S2_MCLK_M1/GPIO4_B6_d |

relógio de gerenciamento GMAC1 |

1,8V |

E/S PARA BAIXO |

|

91 |

GMAC1_MCLKINOUT_M1 |

CIF_CLKIN/EBC_SDCLK/GMAC1_MCLKINOUT_M1/UART1_CTSn_M1/I2S2_SCLK_RX_M1/GPIO4_C1_d |

relógio externo GMAC1 |

1,8V |

E/S PARA BAIXO |

|

92 |

ETH1_REFCLKO_25M_M1 |

I2C4_SCL_M0/EBC_GDOE/ETH1_REFCLKO_25M_M1/SPI3_CLK_M0/I2S2_SDO_M1/GPIO4_B3_d |

Saída de relógio ETH1 |

1,8V |

E/S PARA BAIXO |

|

93 |

GMAC1_RXCLK_M1 |

CIF_D13/EBC_SDDO13/GMAC1_RXCLK_M1/UART7_RX_M2/PDM_SDI3_M1/GPIO4_A3_d |

relógio de recepção GMAC1 |

1,8V |

E/S PARA BAIXO |

|

94 |

GMAC1_RXDV_CRS_M1 |

ISP_PRELIGHT_TRIG/EBC_SDCE3/GMAC1_RXDV_CRS_M1/I2S1_SDO2_M1/GPIO4_B1_d |

Sinal válido de dados GMAC1 RX |

1,8V |

E/S PARA BAIXO |

|

95 |

GMAC1_RXD3_M1 |

CIF_D12/EBC_SDDO12/GMAC1_RXD3_M1/UART7_TX_M2/PDM_SDI2_M1/GPIO4_A2_d |

GMAC1 recebe dados |

1,8V |

E/S PARA BAIXO |

|

96 |

GMAC1_RXD2_M1 |

CIF_D11/EBC_SDDO11/GMAC1_RXD2_M1/PDM_SDI1_M1/GPIO4_A1_d |

GMAC1 recebe dados |

1,8V |

E/S PARA BAIXO |

|

97 |

GMAC1_RXD1_M1 |

CAM_CLKOUT1/EBC_SDCE2/GMAC1_RXD1_M1/SPI3_MISO_M0/I2S1_SDO1_M1/GPIO4_B0_d |

GMAC1 recebe dados |

1,8V |

E/S PARA BAIXO |

|

98 |

GMAC1_RXD0_M1 |

CAM_CLKOUT0/EBC_SDCE1/GMAC1_RXD0_M1/SPI3_CS1_M0/I2S1_LRCK_RX_M1/GPIO4_A7_d |

GMAC1 recebe dados |

1,8V |

E/S PARA BAIXO |

|

99 |

GMAC1_TXCLK_M1 |

CIF_D10/EBC_SDDO10/GMAC1_TXCLK_M1/PDM_CLK1_M1/GPIO4_A0_d |

relógio de transmissão GMAC1 |

1,8V |

E/S PARA BAIXO |

|

100 |

GMAC1_TXEN_M1 |

ISP_FLASHTRIGOUT/EBC_SDCE0/GMAC1_TXEN_M1/SPI3_CS0_M0/I2S1_SCLK_RX_M1/GPIO4_A6_d |

GMAC1 habilitar transmissão |

1,8V |

E/S PARA BAIXO |

|

101 |

GMAC1_TXD3_M1 |

CIF_D9/EBC_SDDO9/GMAC1_TXD3_M1/UART1_RX_M1/PDM_SDI0_M1/GPIO3_D7_d |

GMAC1 transmitir dados |

1,8V |

E/S PARA BAIXO |

|

102 |

GMAC1_TXD2_M1 |

CIF_D8/EBC_SDDO8/GMAC1_TXD2_M1/UART1_TX_M1/PDM_CLK0_M1/GPIO3_D6_d |

GMAC1 transmitir dados |

1,8V |

E/S PARA BAIXO |

|

103 |

GMAC1_TXD1_M1 |

CIF_D15/EBC_SDDO15/GMAC1_TXD1_M1/UART9_RX_M2/I2S2_LRCK_RX_M1/GPIO4_A5_d |

GMAC1 transmitir dados |

1,8V |

E/S PARA BAIXO |

|

104 |

GMAC1_TXD0_M1 |

CIF_D14/EBC_SDDO14/GMAC1_TXD0_M1/UART9_TX_M2/I2S2_LRCK_TX_M1/GPIO4_A4_d |

GMAC1 transmitir dados |

1,8V |

E/S PARA BAIXO |

|

105 |

TP_RST_L_GPIO0_B6 |

I2C2_SDA_M0/SPI0_MOSI_M0/PCIE20_PERSTn_M0/PWM2_M1/GPIO0_B6_u |

Reinicialização do painel de toque |

3,3V |

E/S PARA CIMA

|

|

106 |

TP_INT_L_GPIO0_B5 |

I2C2_SCL_M0/SPI0_CLK_M0/PCIE20_WAKEn_M0/PWM1_M1/GPIO0_B5_u |

Entrada de dados de interrupção do painel de toque |

3,3V |

E/S PARA CIMA |

|

107 |

I2C1_SDA_TP |

I2C1_SDA/CAN0_RX_M0/PCIE20_BUTTONRSTn/MCU_JTAG_TCK/GPIO0_B4_u |

porta serial I2C 1 |

3,3V |

E/S PARA CIMA |

|

108 |

I2C1_SCL_TP |

I2C1_SCL/CAN0_TX_M0/PCIE30X1_BUTTONRSTn/MCU_JTAG_TDO/GPIO0_B3_u |

porta serial I2C 1 |

3,3V |

E/S PARA CIMA |

|

109 |

I2C3_SCL_M0 |

I2C3_SCL_M0/UART3_TX_M0/CAN1_TX_M0/AUDIOPWM_LOUT_N/ACODEC_ADC_CLK/GPIO1_A1_u |

porta serial I2C 3 |

3,3V |

E/S PARA CIMA |

|

110 |

I2C3_SDA_M0 |

I2C3_SDA_M0/UART3_RX_M0/CAN1_RX_M0/AUDIOPWM_LOUT_P/ACODEC_ADC_DATA/GPIO1_A0_u |

porta serial I2C 3 |

3,3V |

E/S PARA CIMA |

|

111 |

I2C2_SCL_M1 |

I2C2_SCL_M1/EBC_SDSHR/CAN2_TX_M0/I2S1_SDO3_M1/GPIO4_B5_d |

porta serial I2C 2 |

1,8V |

E/S PARA BAIXO |

|

112 |

I2C2_SDA_M1 |

I2C2_SDA_M1/EBC_GDSP/CAN2_RX_M0/ISP_FLASH_TRIGIN/VOP_BT656_CLK_M1/GPIO4_B4_d |

porta serial I2C 2 |

1,8V |

E/S PARA BAIXO |

|

113 |

MIPI_CAM1_PDN_L_GPIO3_D3 |

LCDC_D1/VOP_BT656_D1_M0/SPI0_MOSI_M1/PCIE20_WAKEn_M1/I2S1_SCLK_TX_M2/GPIO2_D1_d |

Câmera 1 desligada |

3,3V |

E/S PARA BAIXO |

|

114 |

MIPI_CAM1_RST_L_GPIO3_D2 |

LCDC_D0/VOP_BT656_D0_M0/SPI0_MISO_M1/PCIE20_CLKREQn_M1/I2S1_MCLK_M2/GPIO2_D0_d |

Redefinição da câmera1 |

3,3V |

E/S PARA BAIXO |

|

115 |

MIPI_CAM0_RST_L_GPIO3_D4 |

LCDC_D2/VOP_BT656_D2_M0/SPI0_CS0_M1/PCIE30X1_CLKREQn_M1/I2S1_LRCK_TX_M2/GPIO2_D2_d |

Camera0 redefinir |

3,3V |

E/S PARA BAIXO |

|

116 |

MIPI_CAM0_PDN_L_GPIO3_D5 |

LCDC_D3/VOP_BT656_D3_M0/SPI0_CLK_M1/PCIE30X1_WAKEn_M1/I2S1_SDI0_M2/GPIO2_D3_d |

Desligamento da câmera0 |

3,3V |

E/S PARA BAIXO |

|

117 |

USB2_HOST2_DM |

USB2_HOST2_DM |

USB2_HOST2_DM |

3,3V |

- |

|

118 |

USB2_HOST2_DP |

USB2_HOST2_DP |

USB2_HOST2_DP |

3,3V |

- |

|

119 |

USB2_HOST3_DM |

USB2_HOST3_DM |

USB2_HOST3_DM |

3,3V |

- |

|

120 |

USB2_HOST3_DP |

USB2_HOST3_DP |

USB2_HOST3_DP |

3,3V |

- |

|

121 |

REFCLK_OUT |

REFCLK_OUT/GPIO0_A0_d |

Saída de relógio para câmera |

3,3V |

E/S PARA BAIXO |

|

122 |

CIF_CLKOUT |

CIF_CLKOUT/EBC_GDCLK/PWM11_IR_M1/GPIO4_C0_d |

Saída CIF |

1,8V |

E/S PARA BAIXO |

|

123 |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

1,8V |

- |

|

124 |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

1,8V |

- |

|

125 |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

1,8V |

- |

|

126 |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

1,8V |

- |

|

127 |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

1,8V |

- |

|

128 |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

1,8V |

- |

|

129 |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

1,8V |

- |

|

130 |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

1,8V |

- |

|

131 |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

1,8V |

- |

|

132 |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

1,8V |

- |

|

133 |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

1,8V |

- |

|

134 |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

1,8V |

- |

|

135 |

LCD1_PWREN_H_GPIO0_C5 |

PWM6/SPI0_MISO_M0/PCIE30X2_WAKEn_M0/GPIO0_C5_d |

Ativação de energia do LCD |

3,3V |

E/S PARA BAIXO |

|

136 |

LCD1_BL_PWM5 |

PWM5/SPI0_CS1_M0/UART0_RTSn/GPIO0_C4_d |

Retroiluminação do LCD PWM |

3,3V |

E/S PARA BAIXO |

|

137 |

LCD1_BL_PWM4 |

PWM4/VOP_PWM_M0/PCIE30X1_PERSTn_M0/MCU_JTAG_TRSTn/GPIO0_C3_d |

Retroiluminação do LCD PWM |

3,3V |

E/S PARA BAIXO |

|

138 |

LCD0_PWREN_H_GPIO0_C7 |

HDMITX_CEC_M1/PWM0_M1/UART0_CTSn/GPIO0_C7_d |

Ativação de energia do LCD |

3,3V |

E/S PARA BAIXO |

|

139 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

1,8V |

- |

|

140 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

1,8V |

- |

|

141 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

1,8V |

- |

|

142 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

1,8V |

- |

|

143 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

1,8V |

- |

|

144 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

1,8V |

- |

|

145 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

1,8V |

- |

|

146 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

1,8V |

- |

|

147 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

1,8V |

- |

|

148 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

1,8V |

- |

|

149 |

HDMI_TXCLKN_PORT |

HDMI_TX_CLKN |

HDMI_TX2CLKN_PORT e resistência em série 2.2R |

1,8V |

- |

|

150 |

HDMI_TXCLKP_PORT |

HDMI_TX_CLKP |

HDMI_TXCLKP_PORT e resistência em série 2.2R |

1,8V |

- |

|

151 |

HDMI_TX0N_PORT |

HDMI_TX_D0N |

HDMI_TX0N_PORT e resistência em série 2.2R |

1,8V |

- |

|

152 |

HDMI_TX0P_PORT |

HDMI_TX_D0P |

HDMI_TX0P_PORT e resistência em série 2.2R |

1,8V |

- |

|

153 |

HDMI_TX1N_PORT |

HDMI_TX_D1N |

HDMI_TX1N_PORT e resistência em série 2.2R |

1,8V |

- |

|

154 |

HDMI_TX1P_PORT |

HDMI_TX_D1P |

HDMI_TX1P_PORT e resistência em série 2.2R |

1,8V |

- |

|

155 |

HDMI_TX2N_PORT |

HDMI_TX_D2N |

HDMI_TX2N_PORT e resistência em série 2.2R |

1,8V |

- |

|

156 |

HDMI_TX2P_PORT |

HDMI_TX_D2P |

HDMI_TX2P_PORT e resistência em série 2.2R |

1,8V |

- |

|

157 |

HDMITX_SCL |

HDMITX_SCL/I2C5_SCL_M1/GPIO4_C7_u |

Porta serial I2C para HDMI |

3,3V |

E/S PARA CIMA |

|

158 |

HDMITC_SDA |

HDMITX_SDA/I2C5_SDA_M1/GPIO4_D0_u |

Porta serial I2C para HDMI |

3,3V |

E/S PARA CIMA |

|

159 |

HDMITX_CEC_M0 |

HDMITX_CEC_M0/SPI3_CS1_M1/GPIO4_D1_u |

HDMITX_CEC |

3,3V |

E/S PARA CIMA |

|

160 |

HDMI_TX_HPDIN |

HDMI_TX_HPDIN |

Plugue quente HDMI_TX |

1,8V |

- |

|

161 |

PCIE30X2_CLKREQN_M1 |

LCDC_D4/VOP_BT656_D4_M0/SPI2_CS1_M1/PCIE30X2_CLKREQn_M1/I2S1_SDI1_M2/GPIO2_D4_d |

PCIE30X2_CLKREQn |

3.3 |

E/S PARA BAIXO |

|

162 |

PCIE30X2_WAKEN_M1 |

LCDC_D5/VOP_BT656_D5_M0/SPI2_CS0_M1/PCIE30X2_WAKEn_M1/I2S1_SDI2_M2/GPIO2_D5_d |

PCIE30X2_WAKEn |

3,3V |

E/S PARA BAIXO |

|

163 |

PCIE30X2_PERSTN_M1 |

LCDC_D6/VOP_BT656_D6_M0/SPI2_MOSI_M1/PCIE30X2_PERSTn_M1/I2S1_SDI3_M2/GPIO2_D6_d |

redefinição PCIE30X2 |

3,3V |

E/S PARA BAIXO |

|

164 |

PCIE30X2_PRSNT_L_GPIO2_D7 |

LCDC_D7/VOP_BT656_D7_M0/SPI2_MISO_M1/UART8_TX_M1/I2S1_SDO0_M2/GPIO2_D7_d |

Host de despertar PCIE30X2 |

3,3V |

E/S PARA BAIXO |

|

165 |

PCIE_PWREN_H_GPIO0_D4 |

GPIO0_D4_d |

Ativação de energia PCIE |

1,8V |

E/S PARA BAIXO |

|

166 |

PCIE30_RX1N |

PCIE30_RX1N |

PCIE30_RX1N |

1,8V |

- |

|

167 |

PCIE30_RX1P |

PCIE30_RX1P |

PCIE30_RX1P |

1,8V |

- |

|

168 |

PCIE30_RX0N |

PCIE30_RX0N |

PCIE30_RX0N |

1,8V |

- |

|

169 |

PCIE30_RX0P |

PCIE30_RX0P |

PCIE30_RX0P |

1,8V |

- |

|

170 |

PCIE30_TX1N |

PCIE30_TX1N |

PCIE30_TX1N |

1,8V |

- |

|

171 |

PCIE30_TX1P |

PCIE30_TX1P |

PCIE30_TX1P |

1,8V |

- |

|

172 |

PCIE30_TX0N |

PCIE30_TX0N |

PCIE30_TX0N |

1,8V |

- |

|

173 |

PCIE30_TX0P |

PCIE30_TX0P |

PCIE30_TX0P |

1,8V |

- |

|

174 |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

1,8V |

- |

|

175 |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

1,8V |

- |

|

176 |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

1,8V |

- |

|

177 |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

1,8V |

- |

|

178 |

SATA2_RXN |

PCIE20_RXN/SATA2_RXN/QSGMII_RXN_M1 |

SATA2_RXN |

1,8V |

- |

|

179 |

SATA2_RXP |

PCIE20_RXP/SATA2_RXP/QSGMII_RXP_M1 |

SATA2_RXP |

1,8V |

- |

|

180 |

SATA2_TXN |

PCIE20_TXN/SATA2_TXN/QSGMII_TXN_M1 |

SATA2_TXN |

1,8V |

- |

|

181 |

SATA2_TXP |

PCIE20_TXP/SATA2_TXP/QSGMII_TXP_M1 |

SATA2_TXP |

1,8V |

- |

|

182 |

SATA2_ACT_LED |

EDP_HPDIN_M0/SPDIF_TX_M2/SATA2_ACT_LED/PCIE30X2_PERSTn_M2/I2S3_LRCK_M1/GPIO4_C4_d |

SATA ativo indica |

3,3V |

E/S PARA BAIXO |

|

183 |

USB3_HOST1_SSTXP |

USB3_HOST1_SSTXP/SATA1_TXP/QSGMII_TXP_M0 |

USB3_HOST1_SSTXP |

1,8V |

- |

|

184 |

USB3_HOST1_SSTXN |

USB3_HOST1_SSTXN/SATA1_TXN/QSGMII_TXN_M0 |

USB3_HOST1_SSTXN |

1,8V |

- |

|

185 |

USB3_HOST1_SSRXP |

USB3_HOST1_SSRXP/SATA1_RXP/QSGMII_RXP_M0 |

USB3_HOST1_SSRXP |

1,8V |

- |

|

186 |

USB3_HOST1_SSRXN |

USB3_HOST1_SSRXN/SATA1_RXN/QSGMII_RXN_M0 |

USB3_HOST1_SSRXN |

1,8V |

- |

|

187 |

USB3_HOST1_DM |

USB3_HOST1_DM |

USB3_HOST1_DM |

3,3V |

- |

|

188 |

USB3_HOST1_DP |

USB3_HOST1_DP |

USB3_HOST1_DP |

3,3V |

- |

|

189 |

USB3_OTG0_SSTXP |

USB3_OTG0_SSTXP/SATA0_TXP |

USB3_OTG0_SSTXP |

1,8V |

- |

|

190 |

USB3_OTG0_SSTXN |

USB3_OTG0_SSTXN/SATA0_TXN |

USB3_OTG0_SSTXN |

1,8V |

- |

|

191 |

USB3_OTG0_SSRXP |

USB3_OTG0_SSRXP/SATA0_RXP |

USB3_OTG0_SSRXP |

1,8V |

- |

|

192 |

USB3_OTG0_SSRXN |

USB3_OTG0_SSRXN/SATA0_RXN |

USB3_OTG0_SSRXN |

1,8V |

- |

|

193 |

USB3_OTG0_DM |

USB3_OTG0_DM |

USB3_OTG0_DM |

3,3V |

- |

|

194 |

USB3_OTG0_DP |

USB3_OTG0_DP |

USB3_OTG0_DP |

3,3V |

- |

|

195 |

USB3_OTG0_ID |

USB3_OTG0_ID |

USB3_OTG0_ID |

3,3V |

- |

|

196 |

USB3_OTG0_VBUSDET |

USB3_OTG0_VBUSDET |

USB3_OTG0_VBUS detectar |

3,3V |

- |

|

197 |

USB_HOST_PWREN_H_GPIO0_A6 |

GPU_PWREN/SATA_CP_POD/PCIE30X2_CLKREQn_M0/GPIO0_A6_d |

Ativação de energia do host USB |

3,3V |

E/S PARA BAIXO |

|

198 |

USB_OTG_PWREN_H_GPIO0_A5 |

SDMMC0_PWREN/SATA_MP_SWITCH/PCIE20_CLKREQn_M0/GPIO0_A5_d |

Ativação de energia USB OTG |

3,3V |

E/S PARA BAIXO |

|

199 |

DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

1,8V |

- |

|

200 |

DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

1,8V |

- |

|

201 |

DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

1,8V |

- |

|

202 |

DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

1,8v |

- |

|

203 |

DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

1,8V |

- |

|

204 |

DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

1,8V |

- |

|

205 |

DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

1,8V |

- |

|

206 |

DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

1,8V |

- |

|

207 |

DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

1,8V |

- |

|

208 |

DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

1,8V |

- |

O tamanho é 150mm*110mm, 4 camadas, 1,6mm de espessura.

|

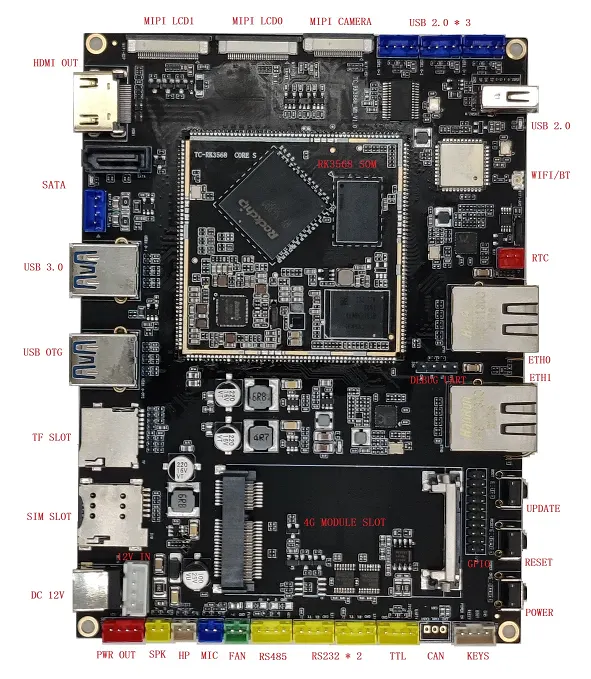

Descrição das interfaces |

|

|

NÃO. |

Nome |

|

ã1ã |

Entrada DC 12V/4 pinos 2,54mm 12V Entrada |

|

ã2ã |

Slot para cartão SIM do módulo 4G |

|

ã3ã |

slot para cartão TF |

|

ã4ã |

USB OTG |

|

ã5ã |

HOST USB3.0 |

|

ã6ã |

Dados SATA |

|

ã7ã |

Saída HDMI |

|

ã8ã |

MIPI LCD1 |

|

ã9ã |

MIPI LCD0 |

|

ã10ã |

Câmera MIPI |

|

ã11ã |

USB 2.0 * 3 |

|

ã12ã |

USB 2.0 Tipo A |

|

ã13ã |

WIFI/BT (AP6335) |

|

ã14ã |

RTC |

|

ã15ã |

ETH0 |

|

ã16ã |

ETH1 |

|

ã17ã |

Atualizar chave |

|

ã18ã |

Botão de reset |

|

ã19ã |

Chave liga/desliga |

|

ã20ã |

Chaves (4 pinos 2,0 mm) |

|

ã21ã |

CAN (3 pinos 2,0 mm) |

|

ã22ã |

Uart TTL (4 pinos 2,0 mm) |

|

ã23ã |

RS232 * 2 (4 pinos 2,0 mm) |

|

ã24ã |

RS485 (4 pinos 2,0 mm) |

|

ã25ã |

VENTILADOR (2 pinos 2,0 mm) |

|

ã26ã |

MIC (2 pinos 2,0 mm) |

|

ã27ã |

HP (2 pinos 2,0 mm) |

|

ã28ã |

SPK (2 pinos 2,0 mm) |

|

ã29ã |

Saída de energia (4 pinos 2,0 mm) |

|

ã30ã |

Depurar Uart (4 pinos 2,0 mm) |

|

ã31ã |

GPIO(2*10pin 2,0mm) |

|

ã32ã |

Slot do Módulo 4G (porta PCIE) |

|

ã33ã |

RK3568 SOM |

A placa usa fonte de alimentação de 12V DC, que se conecta por conector de entrada DC 12V ou conector de entrada de 4 pinos 2,54 mm 12V.

Detalhes de outras interfaces podem se referir ao diagrama esquemático e layout da placa de desenvolvimento.

Considere a placa de desenvolvimento TC-RK3568 como plataforma de hardware, você pode se referir a design de energia, design USB, design de porta PCIE, design de exibição MIPI, design de áudio, design Ethernet, design de câmera e assim por diante. Estes estão abertos aos clientes, podem consultar o nosso design de placa transportadora.

A plataforma de desenvolvimento TC-RK3568 suporta Android11, Linux Buildroot, Ubuntu e Debian System OS, os códigos-fonte são abertos. Você pode ler as referências como o manual do usuário do sistema Thinkcore TC-RK3568.